在今年12月即将于旧金山举行的国际电子元件会议(IEDM)上,英特尔试图重返芯片制造领域的前沿,而代工厂台积电(TSMC)则在定义这一前沿方面迈出了步伐。

台积电的研究人员将公布N2制造工艺,这是一种标称2nm的工艺,专为人工智能(AI)、移动和高性能计算(HPC)领域的计算而设计。另外,英特尔工程师将详细介绍RibbonFET(纳米片晶体管)的缩放情况。

在IEDM会议上,台积电的研究人员预计将报告称,与2022年推出的N3(标称3nm)工艺相比,N2的速度提高15%,功耗降低30%,芯片密度提高15%,甚至更好。

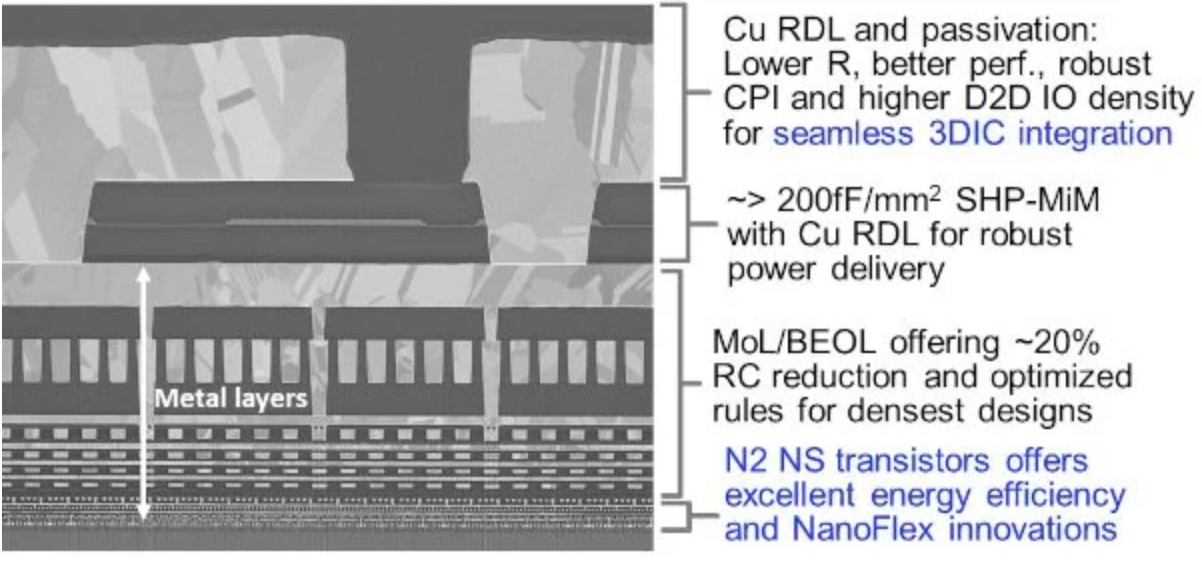

显示铜再分布层的N2互连堆栈截面图(来源IEDM)和T截面图显示,N2平台的铜再分布层 (RDL) 和钝化处理实现了与3D技术的无缝集成。

台积电的G. Yeap等人撰写的论文显示,2nm平台技术采用与3DIC协同优化的高能效纳米片晶体管和互连器件,适用于AI、HPC和移动SoC应用。也将展示具有世界纪录密度38Mbits /平方毫米的SRAM宏。

台积电论文还将详细介绍中段(MEOL)和后端(BEOL)互连,其特点包括:可扩展的铜基再分布层(用于灵活放置输入/输出焊盘,降低阻挡电阻);扁平钝化层(用于提高可靠性);硅通孔(TSV)(用于互连不同层中的设备)。

台积电研究人员表示,N2平台已达到晶圆级可靠性要求,并通过了初步鉴定测试。预计将于2025年通过全面鉴定,并于2026年实现量产。

英特尔的A. Agrawal等在论文中展示了他们如何在不降低电子迁移率的情况下,用6nm栅极和45nm接触多晶硅间距(CPP,晶体管栅极之间的间距)构建纳米片技术(RibbonFET)。

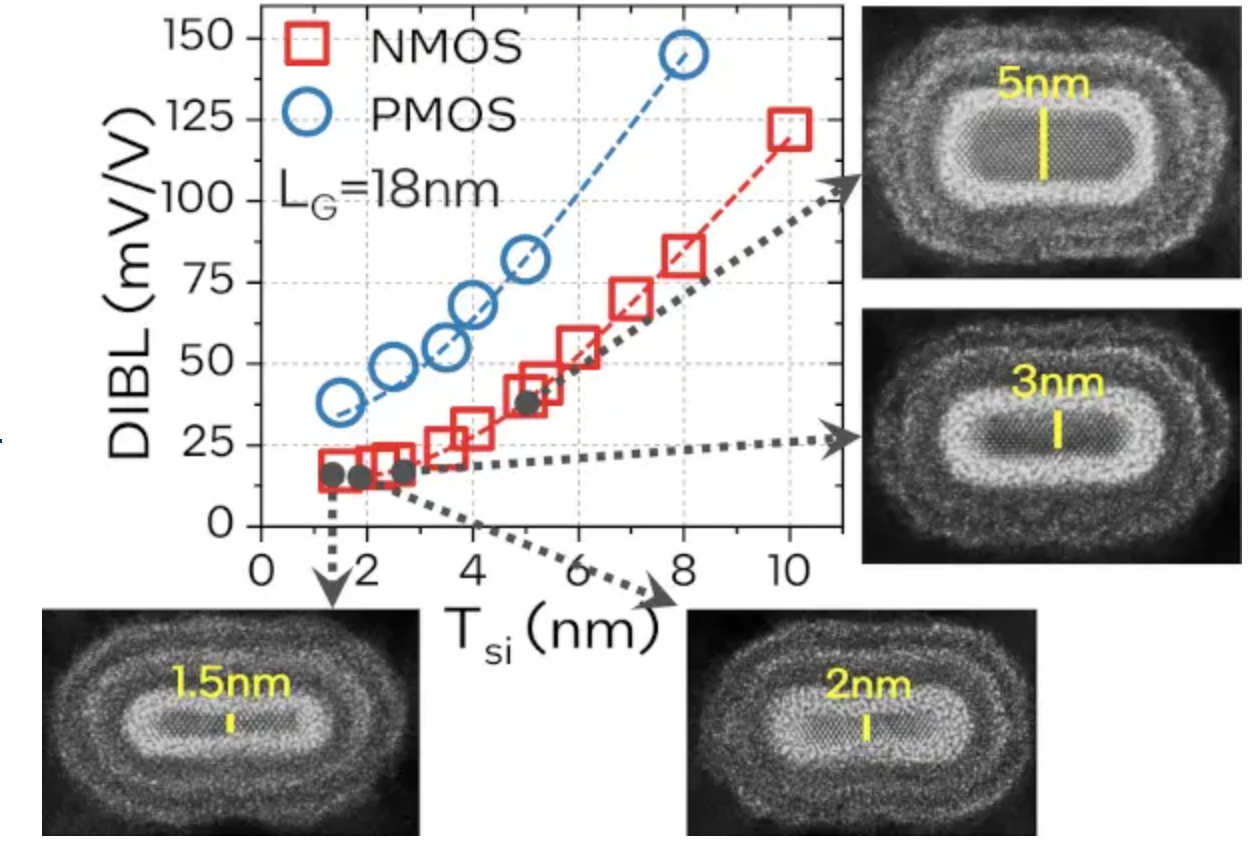

栅极长度为18nm时,漏极诱导势垒降低(DIBL)与硅厚度(Tsi)的关系显示,当Tsi从10nm缩放到1.5nm时,DIBL有所降低;然而,当Tsi <4nm时,DIBL降低达到饱和。与相同Tsi下的NMOS DIBL相比,PMOS DIBL有所提高。图中还显示了1NR晶体管的TEM显微照片,该晶体管的各种Tsi值均低至1.5nm。(来源:IEDM)。

研究人员没有提到英特尔的具体制造工艺,但RibbonFET计划采用Intel 20A工艺(标称20埃或2nm工艺)进行生产。英特尔似乎选择不在Intel 20A工艺上推出任何处理器产品,而是直接从3nm工艺转向Intel 18A(1.8nm)工艺,这可能反映在作者对纳米片缩放的关注上。

英特尔研究人员将证明,在纳米片硅厚度达到3nm之前,电子迁移率不会降低。此后,由于表面粗糙度造成的电子散射将成为一个问题。在论文中,作者报告了4nm以下硅厚度的短通道控制和功函数工程如何实现3nm的低阈值电压。(校对/张杰)